PCIe Driver Design & Development

Project Overview:

Product development and integration involving high performance software has become a necessity for today’s embedded products.

Product development and integration involving high performance software has become a necessity for today’s embedded products.

Designed for a leading manufacturer of PCIe based Video Processing hardware, the project involved development of a Xilinx FPGA based PCI Express (PCIe 3.0) device driver for both Linux and Windows systems.

The prime purpose of the driver is to facilitate high speed bi-directional data transfers of compressed video (Host to Card) and uncompressed decoded video data (Card to Host) over the PCIe 3.0 bus.

Challenges:

The project had its own set of challenges in terms of its complexity and strict delivery schedule needs.

Tools Used:

Have an enquiry ? Please e-mail us at sales@intecoretech.com to know more about our Embedded System Solutions and Services.

Designed for a leading manufacturer of PCIe based Video Processing hardware, the project involved development of a Xilinx FPGA based PCI Express (PCIe 3.0) device driver for both Linux and Windows systems.

The prime purpose of the driver is to facilitate high speed bi-directional data transfers of compressed video (Host to Card) and uncompressed decoded video data (Card to Host) over the PCIe 3.0 bus.

Challenges:

The project had its own set of challenges in terms of its complexity and strict delivery schedule needs.

| Project Challenges | |

|---|---|

|

|

Solution Provided:

Intecore addressed the above challenges with very efficient technical and project management practices and also by engaging with the customer at every step - right from requirements, design, development and testing.

Since the project involved not only the development of a functional PCIe driver but rather a high performance driver for a real-time 4K/UHD video decode application, this made the project all the more challenging.

One of the core/critical modules developed was that of a Scatter Gather DMA (Direct Memory Access) engine for data transfers involving the Host System Memory, the PCIe Endpoint FPGA IP Block and the FPGA internal memory that is accessible to the Video Decode IP Block.

Intecore also helped the customer in the design of a New DMA Block (FPGA) of their own and including some parts of RTL customisation.

Since the project involved not only the development of a functional PCIe driver but rather a high performance driver for a real-time 4K/UHD video decode application, this made the project all the more challenging.

One of the core/critical modules developed was that of a Scatter Gather DMA (Direct Memory Access) engine for data transfers involving the Host System Memory, the PCIe Endpoint FPGA IP Block and the FPGA internal memory that is accessible to the Video Decode IP Block.

Intecore also helped the customer in the design of a New DMA Block (FPGA) of their own and including some parts of RTL customisation.

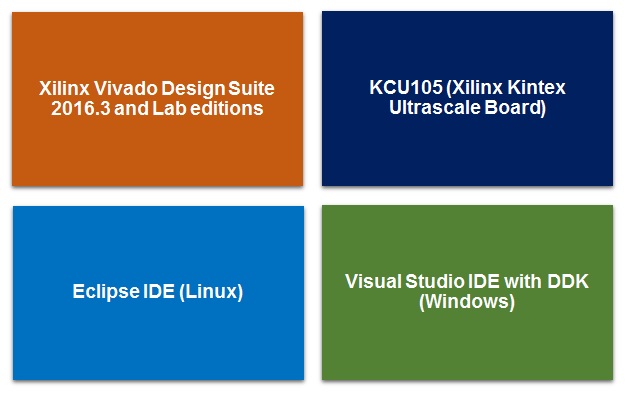

Tools Used:

A multitude of Tools and Platforms were used in the project for both the Host side and the Device (FPGA) side driver development and debug testing.

Most notably, Intecore team quickly ramped up and gained hands-on experience in Xilinx tools - Vivado Design Suite 2016.3 and Vivado Lab editions on KCU105 Xilinx Kintex Ultrascale Board

Eclipse IDE and Visual Studio IDE with DDK were used for Host side driver development and testing.

Most notably, Intecore team quickly ramped up and gained hands-on experience in Xilinx tools - Vivado Design Suite 2016.3 and Vivado Lab editions on KCU105 Xilinx Kintex Ultrascale Board

Eclipse IDE and Visual Studio IDE with DDK were used for Host side driver development and testing.

Result:

The project was delivered successfully and well within the scheduled timelines. Our customer was able to launch the product and put up a great demonstration at NAB'17 show.

Have an enquiry ? Please e-mail us at sales@intecoretech.com to know more about our Embedded System Solutions and Services.